#### Migration von AUTOSAR-basierten Echtzeitanwendungen auf Multicore-Systeme

Michael Bohn / <u>Jörn Schneider</u> / Christian Eltges / Robert Rößger

Fachhochschule Trier

GEFÖRDERT VOM

# News zur Fachhochschule Trier

30. Mai 2011: Sieg in Shell Eco Marathon Europe sowie CO<sub>2</sub>-Award

18. Mai 2011: Promotionsmöglichkeit für FH Trier:

nur 7 FHs bundesweit erhielten

Forschungskolleg

GEFÖRDERT VOM

#### Ausgangssituation

- Existierende Steuergeräte-Software im Kfz

- Entwickelt für Einzelprozessorsysteme

- Verwendet entsprechende Synchronisationsmechanismen

- z.B. Interruptsperren oder Taskprioritäten

- Betriebssystem

- OSEK

- AUTOSAR

- Migration auf Multicore-Systeme

- Jetzt echte Nebenläufigkeit

- → Neue Race Conditions möglich

#### **Migration**

- Standardlösung: Schützen kritischer Abschnitte durch wechselseitigen Ausschluss

- Sind im Einzelprozessorsystem auch geschützt

- Warum funktioniert das nicht im Multicore Fall?

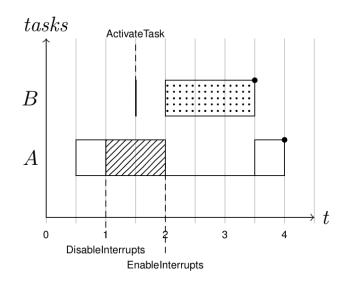

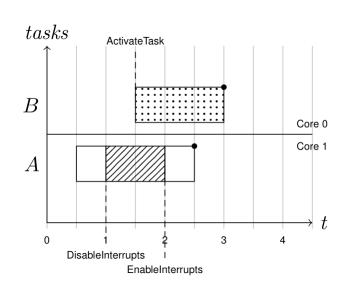

#### Beispiel Interruptsperre:

#### Lösungsidee

- Das Betriebssystem/die Laufzeitumgebung erledigen das

- Probleme:

- 1. Wie werden wechselseitige Ausschlüsse auf Multicore Systemen realisiert?

- 2. Welche wechselseitigen Ausschlüsse müssen gewahrt bleiben?

# Seitenblick: Realisierung auf Multicore Systemen

- AUTOSAR: nur Spinlocks

- Potentielle Deadlocks

- Potentielle Verschwendung von Rechenzeit

- Priority Inversion

- Unbounded Remote Blocking

- Untersuchung echtzeitfähiger Alternativen in Arbeit

- Simulator: SimTrOS

#### Welche wechselseitigen Ausschlüsse müssen gewahrt bleiben?

- Alle?

- Problem: Viele wechselseitige Ausschlüsse ergeben sich auf Einzelprozessoren ungewollt

- Konsequenz: Parallelität nicht nutzbar!

- → Keine sinnvolle Lösung

- Also nur die Notwendigen!

- Welche sind notwendig?

- Wie wird das ermittelt?

# Unsere Lösung: Automatisierung über zweistufiges Analysewerkzeug

# Phase I: Ermitteln kritischer Abschnitte

- Mittels statischer Programm-Analyse

- Bsp.

- Interruptsperre

- Get-/ReleaseResource

- Eigens entwickelte flow-sensitive, generische API-Call Paar Analyse auf Hochsprachenebene

```

#include "util.h"

#include "MotorB.h"

extern int gSensorAData[2];

extern int gSensorBData[2];

static int motorB;

TASK(MotorB) {

int v1, v2, v3, v4;

10

11

12

GetResource(rSensorAData);

13

GetResource(rSensorBData);

v1 = gSensorAData[0];

14

15

v2 = gSensorAData[1];

v3 = gSensorBData[0];

16

v4 = gSensorBData[1];

17

ReleaseResource(rSensorBData);

ReleaseResource(rSensorAData);

19

20

21

motorB = v1 & v2 & v3 & v4;

TerminateTask():

23

```

#### Analyseeigenschaften

- Analyse findet mindestens alle vorhandenen wechselseitigen Ausschlüsse (WA)

- Zwei Arten von Pessimismus:

- Vermeintliche WA

- Überapproximation der Analyse (False Positives)

- Vorhandene aber unnötige WA

- Kollateralschaden, z.B. Interruptsperre

- Wie Pessimismus reduzieren?

# Phase II: Reduktion der Einschränkungen

- Speicherzugriffsanalyse

- Value Analyzer von AbsInt GmbH

- Wenn kein geteilter Speicher zwischen Programmabschnitten

- → kein Grund für WA aus Programmsemantik erkennbar

- Achtung: Gründe abseits der Semantik sind möglich

- Bsp. 2 Aktoren dürfen sich nicht gleichzeitig bewegen

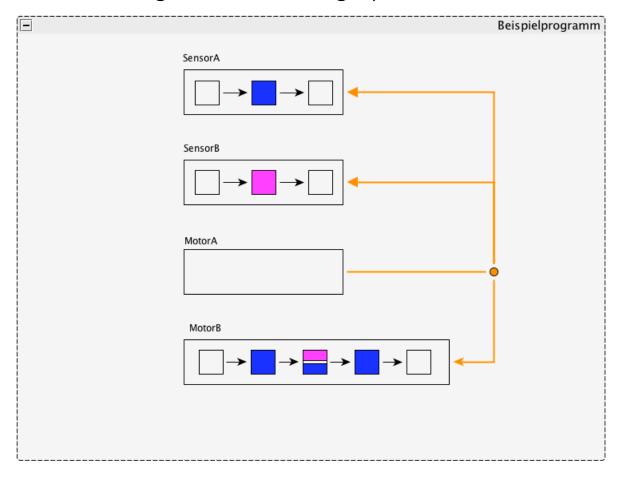

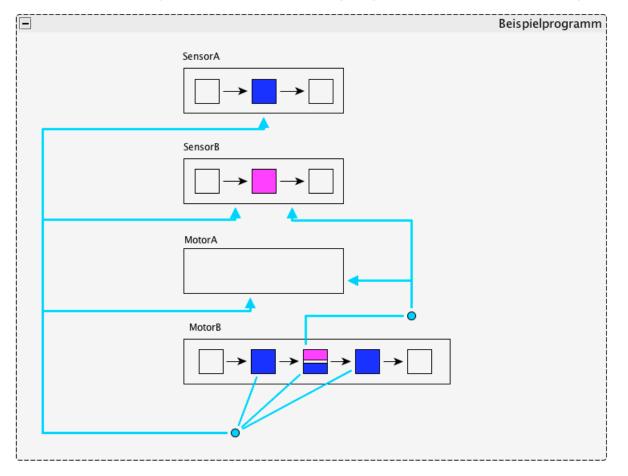

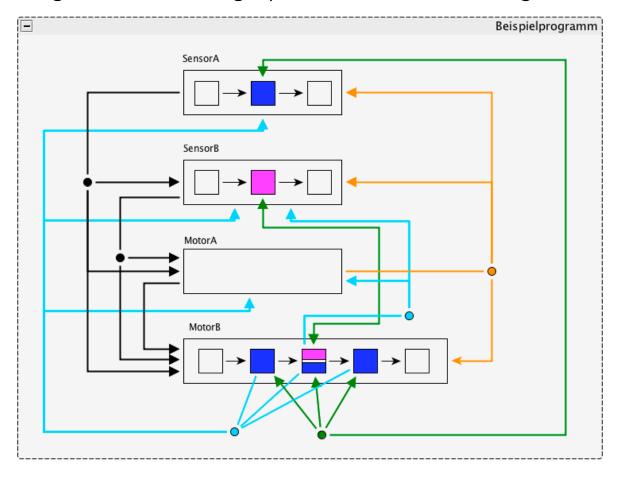

# Analyseablauf im Beispiel

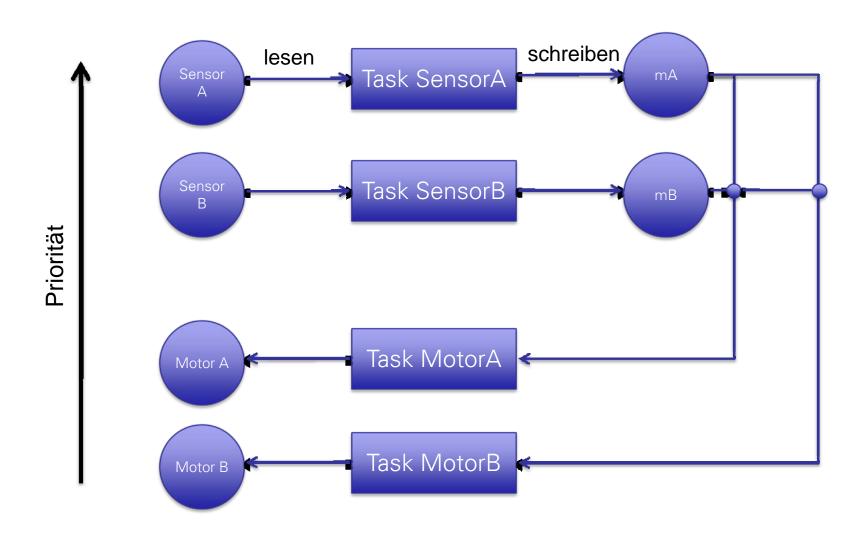

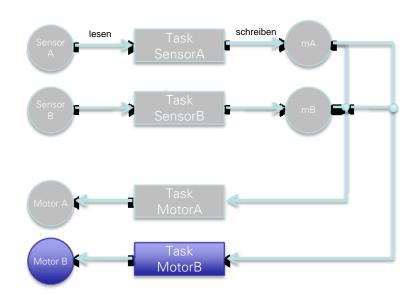

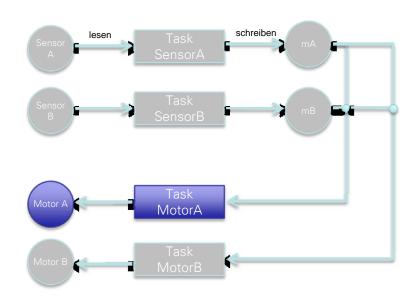

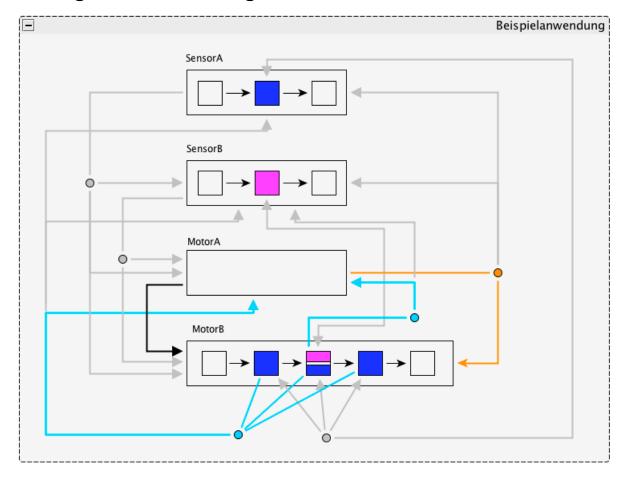

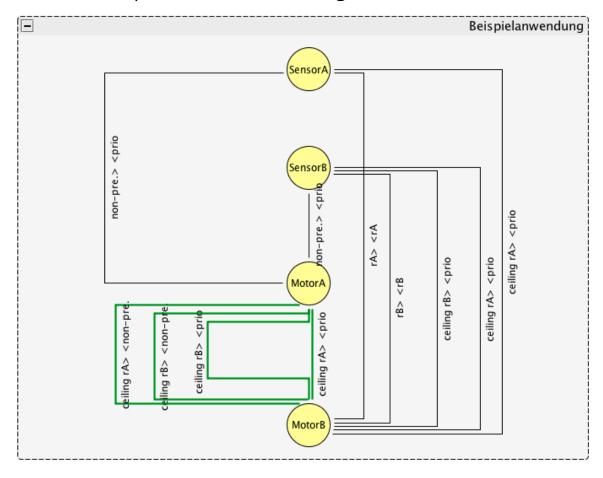

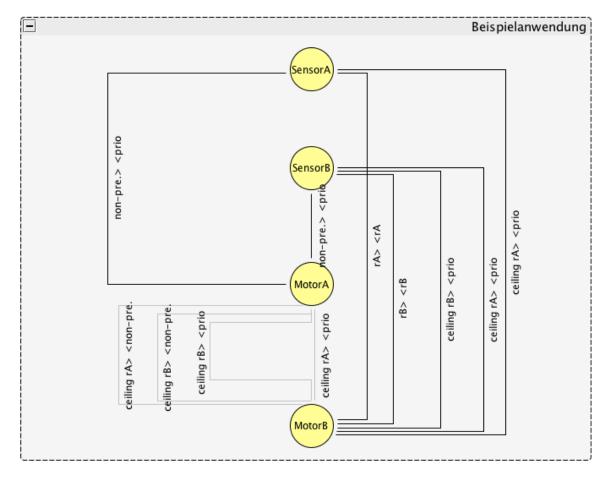

#### Beispielanwendung

#### Beispielanwendung

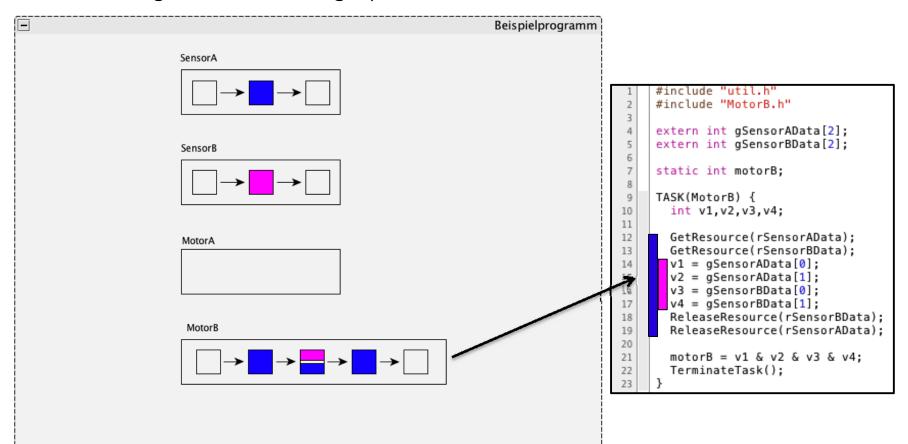

Wechselseitiger Ausschluss – Task MotorB

```

#include "util.h"

#include "MotorB.h"

extern int gSensorAData[2];

4

extern int gSensorBData[2];

5

6

static int motorB;

7

TASK(MotorB) {

int v1, v2, v3, v4;

10

11

GetResource(rSensorAData);

12

GetResource(rSensorBData);

13

v1 = gSensorAData[0];

14

v2 = gSensorAData[1];

v3 = gSensorBData[0];

16

v4 = gSensorBData[1];

ReleaseResource(rSensorBData);

18

ReleaseResource(rSensorAData);

19

20

21

motorB = v1 & v2 & v3 & v4;

TerminateTask();

22

23

```

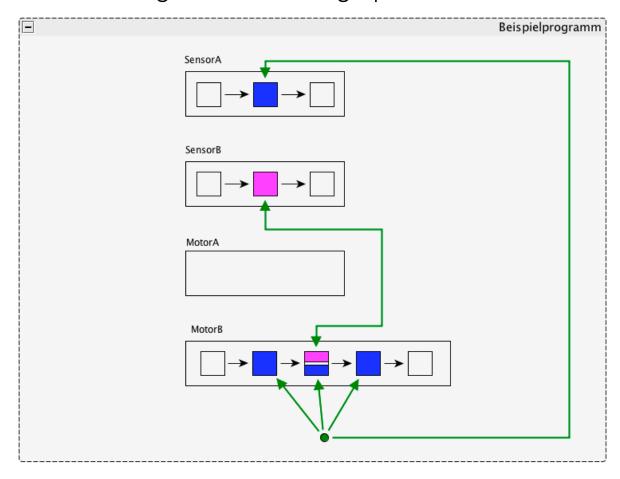

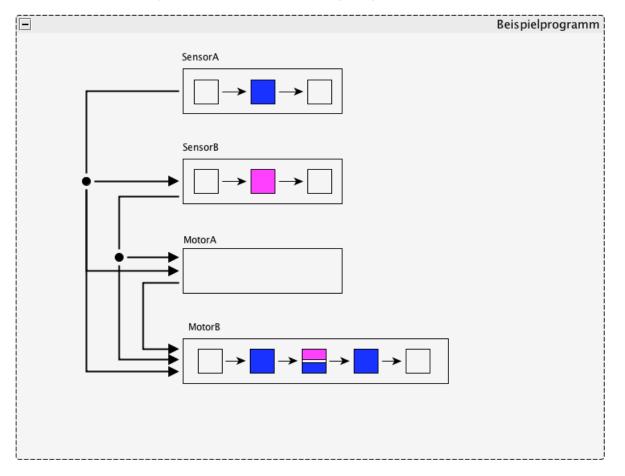

#### Beispielanwendung

Wechselseitiger Ausschluss – Task MotorA

```

Non-Preemptive

#include "util.h"

#include "MotorA.h"

extern int gSensorAData[2];

4

extern int gSensorBData[2];

5

6

static int motorA;

7

8

TASK(MotorA) {

int v1 = gSensorAData[0];

10

int v2 = gSensorAData[1];

11

int v3 = gSensorBData[0];

12

int v4 = gSensorBData[1];

13

14

15

motorA = v1 \& v2 \& v3 \& v4;

16

TerminateTask();

}

17

18

```

- Ermittlung aller vorhandenen einseitigen Ausschlüsse

- OSEK/AUTOSAR-Mechanismen:

- höhere Priorität

- Basispriorität

- Priority-Ceiling

- Nichtunterbrechbarkeit

- gleiche Taskpriorität

- Ressourcenmechanismus

- Interruptsperre

→ OIL/XML

- → OIL/XML

- → OIL/XML

- → statische Programmanalyse + OIL/XML

- → statische Programmanalyse

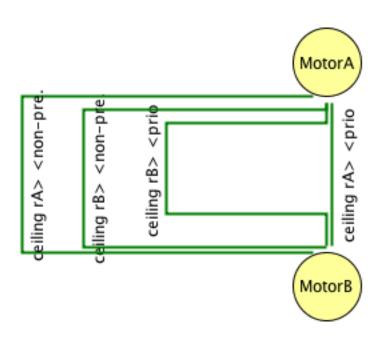

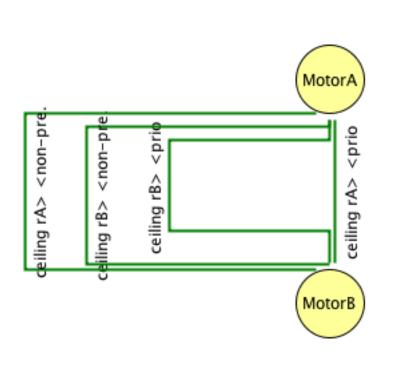

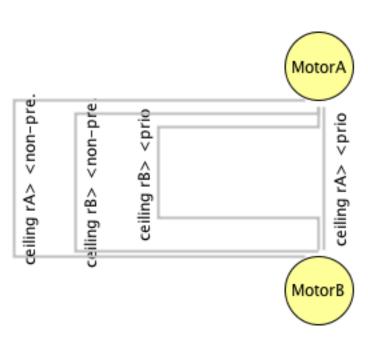

Einseitiger Ausschlussgraph (EAG) - Basis

• Einseitiger Ausschlussgraph (EAG) - Ressourcen

Wechselseitiger Ausschluss über Ressourcenmechanismus

Einseitiger Ausschlussgraph (EAG) – höhere Priorität

Einseitiger Ausschluss über höhere Priorität

• Einseitiger Ausschlussgraph (EAG) - Nichtunterbrechbarkeit

Einseitiger Ausschluss über Nichtunterbrechbarkeit

Einseitiger Ausschlussgraph (EAG) – Priority Ceiling

**Einseitiger Ausschluss** über Priority Ceiling

• Einseitiger Ausschlussgraph (EAG) – Gesamtergebnis

Ermittlung wechselseitiger Ausschlüsse

Constraint Graph (Extraktionsergebnis)

### Relevante Speicherzugriffe MotorA

| Berenisaar. |   | Datenadr.  |

|-------------|---|------------|

| 0x400021c8  | R | 0x400060b8 |

| 0x400021cc  | R | 0x400060bc |

| 0x400021d0  | R | 0x400060c8 |

| 0x400021d4  | R | 0x400060cc |

| 0x400021e4  | W | 0x400060d0 |

| Relevante Speicherzugriffe MotorA |   |            |  |  |  |

|-----------------------------------|---|------------|--|--|--|

| Befehlsadr.                       |   | Datenadr.  |  |  |  |

| 0x400021c8                        | R | 0x400060b8 |  |  |  |

| 0x400021cc                        | R | 0x400060bc |  |  |  |

| 0x400021d0                        | R | 0x400060c8 |  |  |  |

| 0x400021d4                        | R | 0x400060cc |  |  |  |

| 0x400021e4                        | W | 0x400060d0 |  |  |  |

| Relevante opercherzugnine Motorb |   |            |  |  |

|----------------------------------|---|------------|--|--|

| Befehlsadr.                      |   | Datenadr.  |  |  |

| 0x4000222c                       | R | 0x400034a0 |  |  |

| 0x40002238                       | R | 0x400034a4 |  |  |

| 0x40002240                       | R | 0x400060b8 |  |  |

| 0x40002244                       | R | 0x400060bc |  |  |

| 0x40002248                       | R | 0x400060c8 |  |  |

| 0x4000224c                       | R | 0x400060cc |  |  |

| 0x40002254                       | R | 0x400034a4 |  |  |

| 0x40002260                       | R | 0x400034a0 |  |  |

| 0x40002274                       | W | 0x400060d4 |  |  |

|                                  |   |            |  |  |

Relevante Speicherzugriffe MotorB

Überlappende Zugriffe nur lesend

**→**

WA-Einschränkungen für Schutz Speicherzugriffe nicht notwendig!

| Relevante Speicherzugnine MotorA |      |            |  |  |

|----------------------------------|------|------------|--|--|

| Befehlsadr.                      |      | Datenadr.  |  |  |

| 0x400021c8                       | R    | 0x400060b8 |  |  |

| 0x400021cc                       | R    | 0x400060bc |  |  |

| 0x400021d0                       | R    | 0x400060c8 |  |  |

| 0x400021d4                       | R    | 0x400060cc |  |  |

| 0x400021e4                       | \/\/ | 0x400060d0 |  |  |

Polovanto Spoicharzuariffo MotorA

Polovanta Spaicharzugriffa MotorP

| Relevante Speicherzugnille Motorb |   |            |  |  |

|-----------------------------------|---|------------|--|--|

| Befehlsadr.                       |   | Datenadr.  |  |  |

| 0x4000222c                        | R | 0x400034a0 |  |  |

| 0x40002238                        | R | 0x400034a4 |  |  |

| 0x40002240                        | R | 0x400060b8 |  |  |

| 0x40002244                        | R | 0x400060bc |  |  |

| 0x40002248                        | R | 0x400060c8 |  |  |

| 0x4000224c                        | R | 0x400060cc |  |  |

| 0x40002254                        | R | 0x400034a4 |  |  |

| 0x40002260                        | R | 0x400034a0 |  |  |

| 0x40002274                        | W | 0x400060d4 |  |  |

|                                   |   |            |  |  |

Wechselseitige Ausschlüsse:

Vor Reduktion: 11 Nach Reduktion: 7

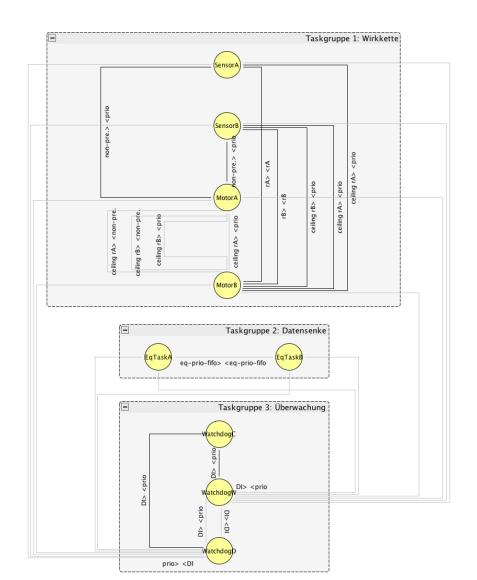

#### Größeres Beispiel

Wechselseitige Ausschlüsse:

Vor Reduktion: 31 Nach Reduktion: 9

#### **Fazit**

- Migration auf Multicore führt zu neuen Race Conditions

- Abhilfe:

- Finden aller wechselseitigen Ausschlüsse

- Bewerten aller wechselseitigen Ausschlüsse

- Lösung:

- Automatisierung durch zweistufigen Analyseansatz

#### Kooperationspartner:

AbsInt GmbH

Prof. Reinhard Wilhelm, Universität des Saarlandes